Les logiciels de test ScanPlus sont des applications 32-bit compatible Windows 95, 98

et NT comportants plusieurs éléments:

Les logiciels proposés sont les suivants :

La figure ci-dessous montre la fonctionnalité de ces différents logiciels ainsi que

leurs interactions.

Le but premier de ces logiciels est donc de tester une carte électronique. Il existe 5

types de test

Le test de l’infrastructure permet de vérifier que le Test Access Port (TAP) est correctement relié aux composants JTAG. Cela signifie qu’il va vérifier que la chaîne de scan est établie correctement. Il s’agit donc de la première étape à réaliser.

Test des interconnections :Le test des interconnections vérifie que les connections entre les différents composants JTAG sont correctement réalisées. Il va donc pouvoir détecter des circuits ouverts, des courts-circuits, de mauvaises soudures, des circuits mal alignés …

Test du Buswire :Le test du buswire est utilisé lorsque des drivers de bus sont présents sur la carte.

Il test donc les driver un par un, ainsi que toutes leurs opérations (receivers, drivers,

bi-directionnel). Différents bus sont testés en parallèle.

Le test des clusters permet de tester les composants non JTAG entourés des composants JTAG d’une carte électronique. En fait, dans ce contexte, les cellules JTAG agissent comme des récepteurs pour tester les composants ‘non JTAG’ (en général, il s’agit de portes logiques).

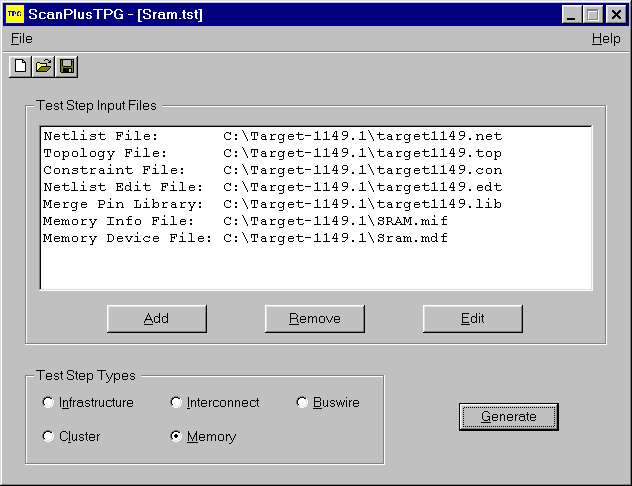

Ce test permet de tester toutes les broches de la mémoire ainsi que ses connexions. L'utilisateur fournit une description de la mémoire à tester (bus d'adresse, bus de donnée, bus de contrôle) et le compilateur génère une série de vecteurs de test (Memory Pattern Generator) à appliquer sur la carte.

Après avoir vu quels types de test il est possible de réaliser avec la gamme ScanPlus, nous étudions maintenant chacun de ces logiciels en expliquant leur rôle d’une part et leur fonctionnement d’autre part. Cependant étant donné que chacun de ces logiciels nécessitent un certain nombre de fichiers pour leur fonctionnement (soit directement, soit indirectement), nous allons auparavant nous intéresser à l’étude de ces fichiers.

Les différents fichiers :Différents types de fichiers sont nécessaires pour la génération des vecteurs de test (ScanPlus TPG).Vous pourrez trouver leur description ainsi qu’un exemple.

Les fichiers Netlist (*.net) :Ce fichier doit contenir la description de toutes les broches et des nœuds de la carte électronique. Les logiciels de la gamme ScanPlus acceptent la pluspart des fichiers du type CAE/CAD.

Les fichiers BSDL (*.bsd) :Les fichiers BSDL sont des fichiers donnés par le constructeur du composant JTAG et contiennent toutes les informations relatives à celui-ci. Ils sont écrits en Boundary-Scan Description Language (BSDL) qui est un dérivé du VHSIC Hardware Description Language (VHDL).

Exemple d’un fichiers BSDL d’une bascule D (la 74bct8374) :

entity ttl74bct8374 is

generic (PHYSICAL_PIN_MAP : string := "DW_PACKAGE");

port (CLK:in bit; Q:out bit_vector(1 to 8); D:in bit_vector(1 to 8);

GND, VCC:linkage bit; OC_NEG:in bit; TDO:out bit; TMS, TDI, TCK:in bit);

use STD_1149_1_1990.all; -- Get Std 1149.1-1990 attributes and definitions

attribute PIN_MAP of ttl74bct8374 : entity is PHYSICAL_PIN_MAP;

constant DW_PACKAGE:PIN_MAP_STRING:="CLK:1, Q:(2,3,4,5,7,8,9,10), " &

"D:(23,22,21,20,19,17,16,15)," & "GND:6, VCC:18, OC_NEG:24, TDO:11, TMS:12, TCK:13,TDI:14";

constant FK_PACKAGE:PIN_MAP_STRING:="CLK:9, Q:(10,11,12,13,16,17,18,19)," &

"D:(6,5,4,3,2,27,26,25)," & "GND:14, VCC:28, OC_NEG:7, TDO:20, TMS:21, TCK:23, TDI:24";

attribute TAP_SCAN_IN of TDI : signal is true;

attribute TAP_SCAN_MODE of TMS : signal is true;

attribute TAP_SCAN_OUT of TDO : signal is true;

attribute TAP_SCAN_CLOCK of TCK : signal is (20.0e6, BOTH);

attribute INSTRUCTION_LENGTH of ttl74bct8374 : entity is 8;

attribute INSTRUCTION_OPCODE of ttl74bct8374 : entity is

"BYPASS (11111111, 10001000, 00000101, 10000100, 00000001)," &

"EXTEST (00000000, 10000000)," &

"SAMPLE (00000010, 10000010)," &

"INTEST (00000011, 10000011)," &

"TRIBYP (00000110, 10000110)," & -- Boundary Hi-Z

"SETBYP (00000111, 10000111)," & -- Boundary 1/0

"RUNT (00001001, 10001001)," & -- Boundary run test

"READBN (00001010, 10001010)," & -- Boundary read normal

"READBT (00001011, 10001011)," & -- Boundary read test "CELLTST(00001100, 10001100)," & -- Boundary selftest normal"TOPHIP (00001101, 10001101)," & -- Boundary toggle out test

"SCANCN (00001110, 10001110)," & -- BCR Scan normal

"SCANCT (00001111, 10001111)"; -- BCR Scan test

attribute INSTRUCTION_CAPTURE of ttl74bct8374 : entity is

"10000001";

attribute INSTRUCTION_DISABLE of ttl74bct8374 : entity is "TRIBYP";

attribute REGISTER_ACCESS of ttl74bct8374 : entity is

"BOUNDARY (READBN, READBT, CELLTST)," &

"BYPASS (TOPHIP, SETBYP, RUNT, TRIBYP)," &

"BCR[2] (SCANCN, SCANCT)"; -- 2-bit Boundary Control Register

attribute BOUNDARY_CELLS of ttl74bct8374 : entity is "BC_1";

attribute BOUNDARY_LENGTH of ttl74bct8374 : entity is 18;

attribute BOUNDARY_REGISTER of ttl74bct8374 : entity is

-- num cell port function safe [ccell disval rslt]

"17 (BC_1, CLK, input, X)," &

"16 (BC_1, OC_NEG, input, X)," & -- Merged Input/Control

"16 (BC_1, *, control, 1)," & -- Merged Input/Control

"15 (BC_1, D(1), input, X)," &

"14 (BC_1, D(2), input, X)," &

"13 (BC_1, D(3), input, X)," &

"12 (BC_1, D(4), input, X)," &

"11 (BC_1, D(5), input, X)," &

"10 (BC_1, D(6), input, X)," &

"9 (BC_1, D(7), input, X)," &

"8 (BC_1, D(8), input, X)," &

"7 (BC_1, Q(1), output3, X, 16, 1, Z)," & -- cell 16 @ 1 -> Hi-Z.

"6 (BC_1, Q(2), output3, X, 16, 1, Z)," &

"5 (BC_1, Q(3), output3, X, 16, 1, Z)," &

"4 (BC_1, Q(4), output3, X, 16, 1, Z)," &

"3 (BC_1, Q(5), output3, X, 16, 1, Z)," &

"2 (BC_1, Q(6), output3, X, 16, 1, Z)," &

"1 (BC_1, Q(7), output3, X, 16, 1, Z)," &

"0 (BC_1, Q(8), output3, X, 16, 1, Z)";

end ttl74bct8374;

Comme son nom l’indique ce logiciel permet de générer les vecteurs de test de la carte.

Le compilateur contenu dans ce logiciel est un compilateur Hewlett-Packard (HP3070). C’est donc un produit de qualité dont la vitesse d’action étonne les utilisateurs car la durée des tests est de l’ordre de quelques secondes (Cette vitesse d’action n’est donnée qu’à titre indicatif puisqu’elle va évidemment varier en fonction de la carte à tester).

ScanPlus TPG convertit tous les fichiers dont il a besoin (son besoin en fichier dépends du type de test que l’on souhaite réaliser) pour n’en former qu’un seul du type compact vector format (CVF). Ce fichier du type compact vector format est donc le fichier qui contient les vecteurs de test correspondant au type de test que l’on souhaite réaliser. ScanPlus TPG va donc générer 5 vecteurs de test au maximum correspondant à chacun des 5 tests décris dans la partie précédente. Afin de générer ces vecteurs de test, ScanPlus TPG passe par la création de fichiers intermédiaires.

Ce logiciel fait partie des logiciels optionnels puisqu’Elexience propose à ses clients de réaliser elle-même cette étape. En réalité cela n’est rentable pour le client que s’il n’envisage de réaliser que très peu d’applications (au-delà de 2 ou 3 applications, il devient plus avantageux de faire l’acquisition de ce logiciel).

Une fois les vecteurs de tests générés, il devient possible de tester la carte électronique en appliquant ces vecteurs de test à la carte électronique. C’est le rôle que va jouer ScanPlus Runner.

La liaison entre la carte électronique à tester et le poste de travail se fait par l’intermédiaire du bus JTAG.

ScanPlus Runner est en fait un des logiciels phare de la gamme de Corelis puisque c’est le logiciel qui permet d’appliquer sur la carte à tester les vecteurs de test générés par ScanPlus TPG. Il permet trois modes de diagnostic :

Avec ce type de diagnostic, ScanPlus Runner vérifie le fonctionnement de la carte sans rentrer dans les détails. Il renvoie simplement à l’utilisateur si le test qu’il a effectué est passé ou non.

Lorsque l’utilisateur sélectionne ce type de fonctionnement l’idée est la même que précédemment mais s’il y a dysfonctionnement, il permet de visualiser la table de vérité donc d’en déduire d’où provient ce dysfonctionnement.

Pour ce mode de fonctionnement, ScanPlus Runner va effectuer exactement les mêmes tests que précédemment mais en cas de dysfonctionnement, il va indiquer précisément d’où provient ce dysfonctionnement et les manipulations possibles à effectuer par l’utilisateur pour le faire disparaître.

De plus ScanPlus Runner intègre la fonction In-System-Programming (ISP) permettant le téléchargement de programme à l'intérieur de circuits programmables (FPAG's, CPLD's, ASIC's) de toutes marques au format SVF ou JAM. Il permet également de programmer les mémoires FLASH à l'aide du fichier généré par ScanPlus Flash Generator.

ScanPlus Runner propose également en standard des drivers de haut niveau (Labwindows CVI, Labview et programmation en ligne) afin de créer sa propre interface de test.

ScanPlus Debugger permet de venir regarder la valeur de la sortie d’une ou d’un groupement de broches (dans ce cas il y a donc création d’un bus) en fonction de la valeur que l’utilisateur a décidé de lui appliquer en entrée. Cette valeur peut être obtenue aussi bien en binaire, qu’en décimal mais également en hexadécimal. D’où son nom de ScanPlus Debugger puisqu’on peut debugger virtuellement la carte et appliquer ces modifications lors de la mise au point de nouveaux prototypes. Un test d'infrastructure est également disponible.

ScanPlus Flash fait partie des logiciels qui utilisent d’autres fonctions du bus JTAG que le test. En effet ce logiciel utilise le bus JTAG pour le téléchargement de données (code) à l’intérieure de mémoires Flash.

Corelis propose dans sa gamme d’autres types de matériel comme des émulateurs ou des boîtiers permettant de créer des Entrées/Sorties que l’on intègre directement dans la chaîne JTAG.